LLVM之父Chris Lattner:编译器的黄金时代

发布于:2022-04-26 16:07

|

阅读数:662

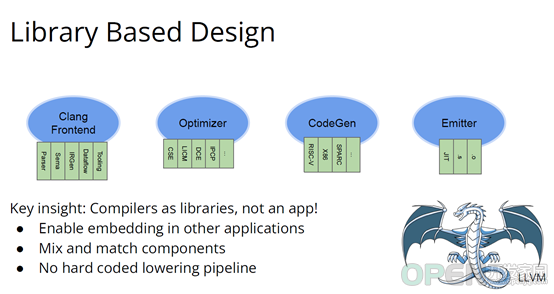

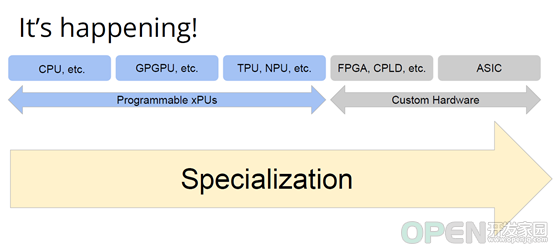

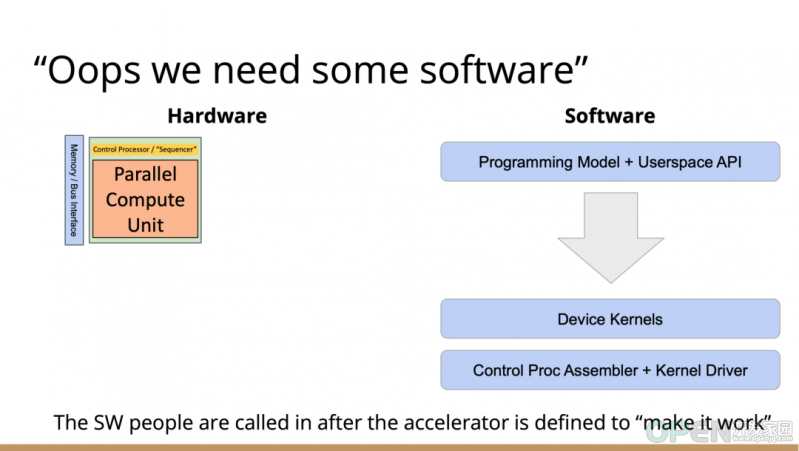

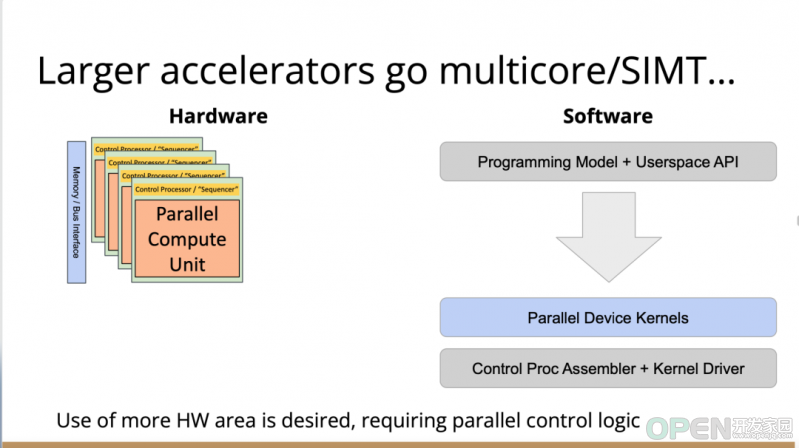

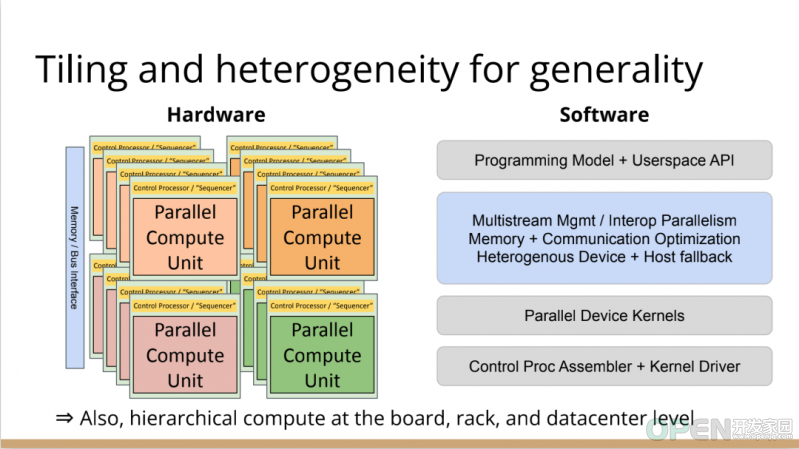

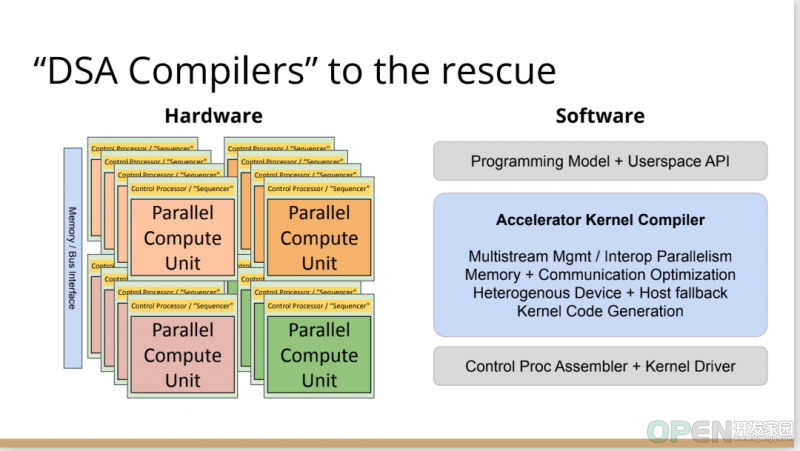

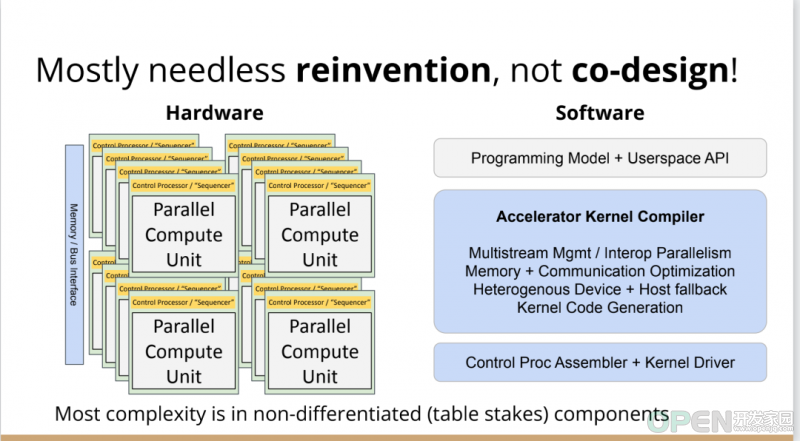

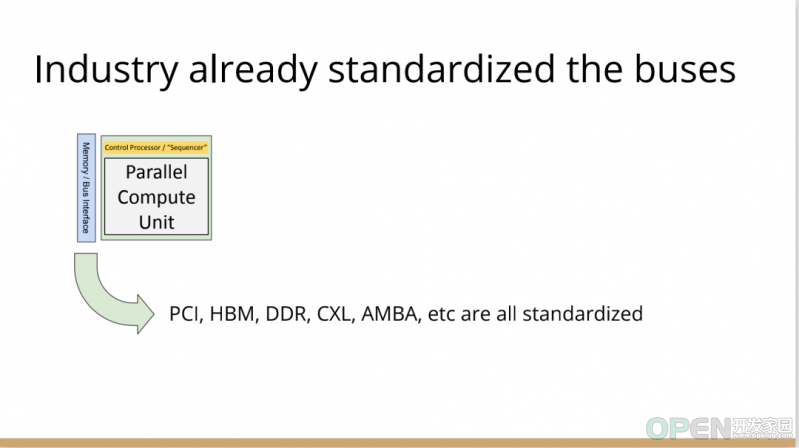

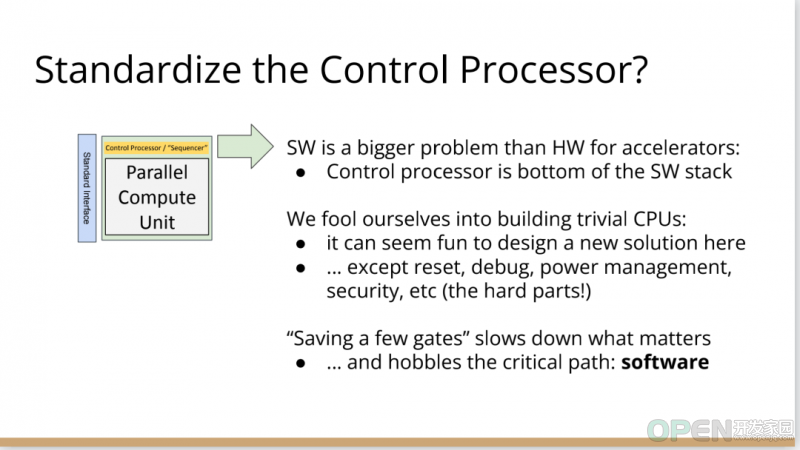

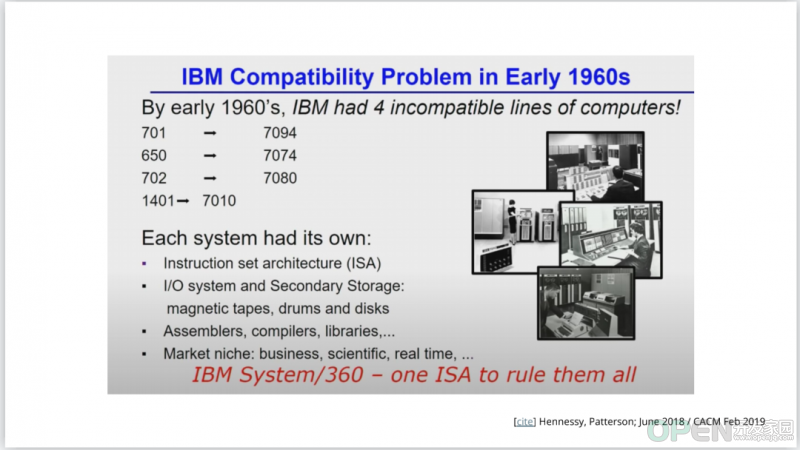

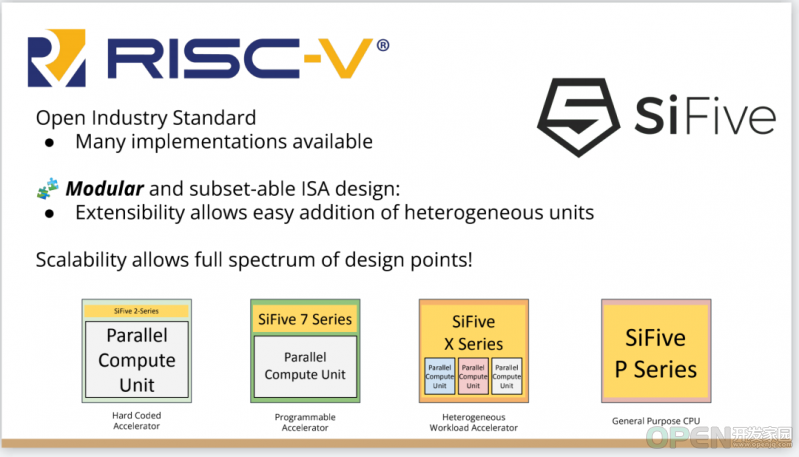

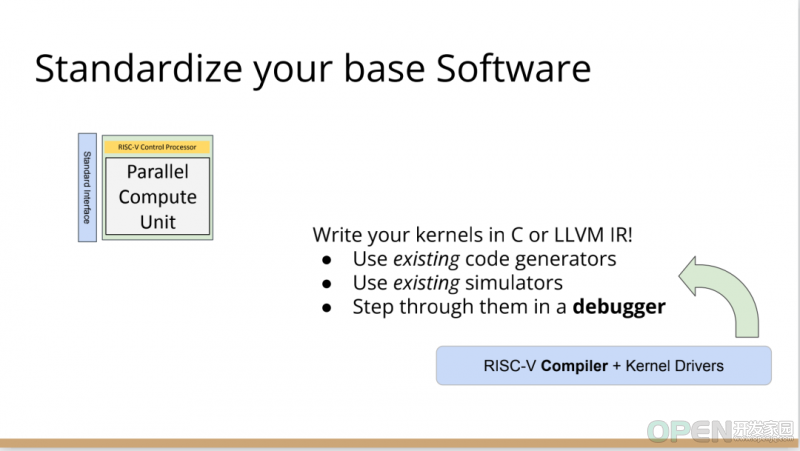

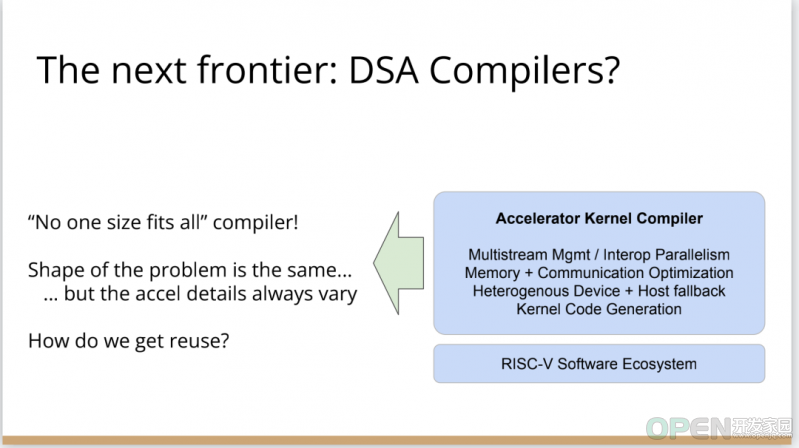

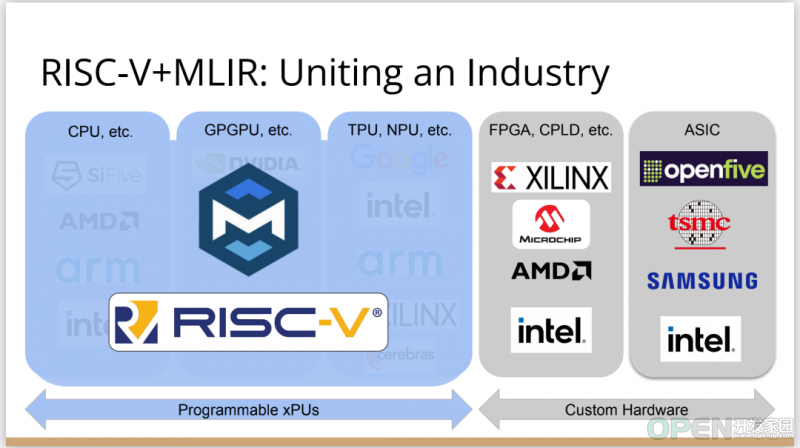

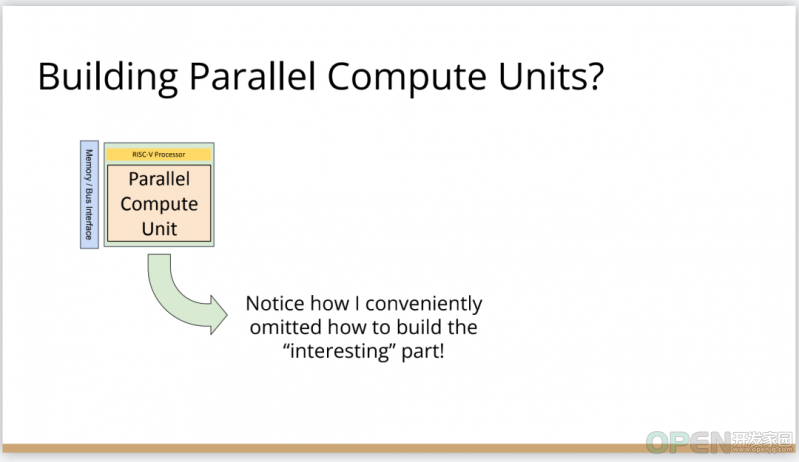

|

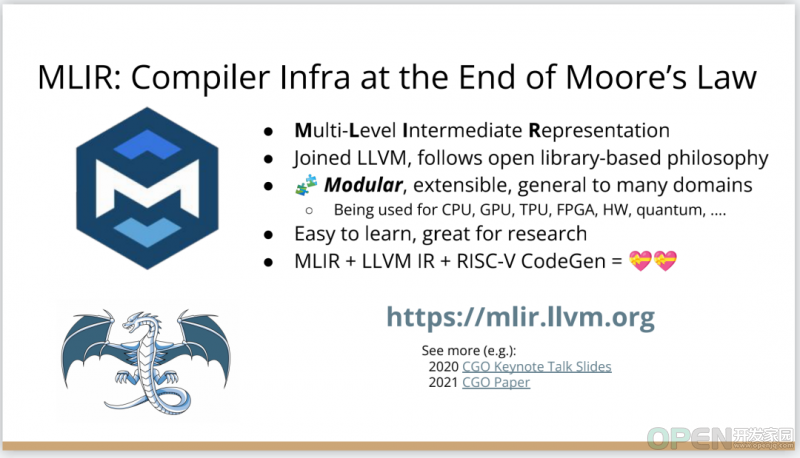

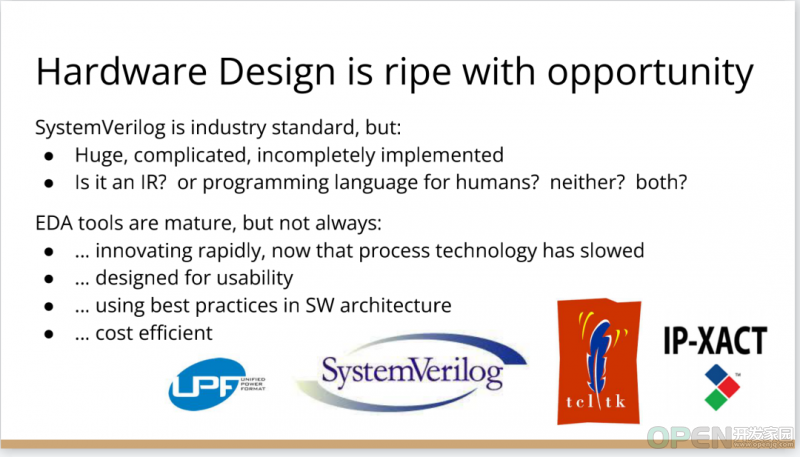

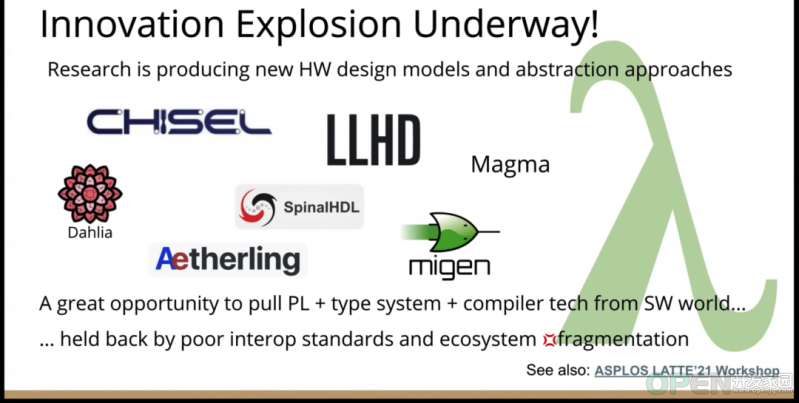

评论:0

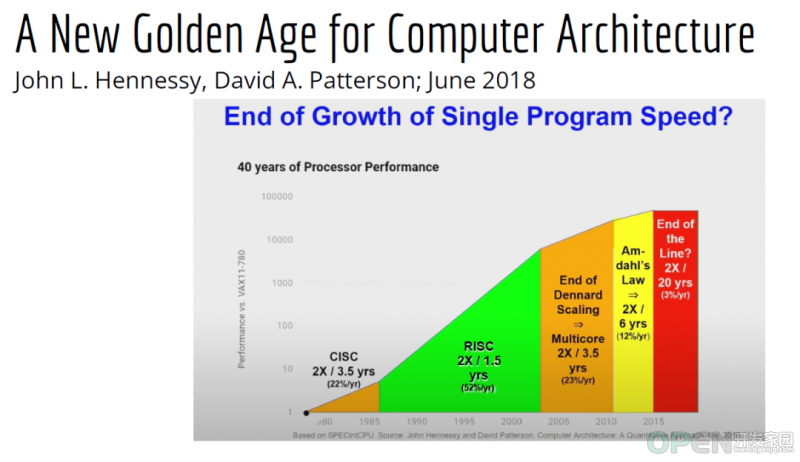

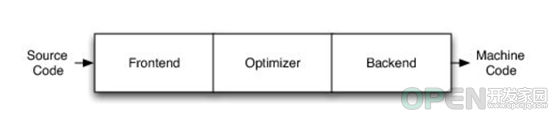

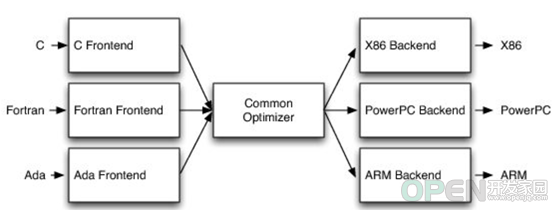

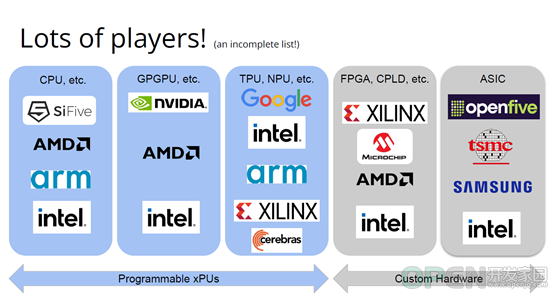

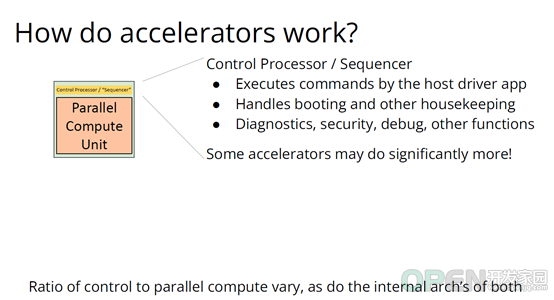

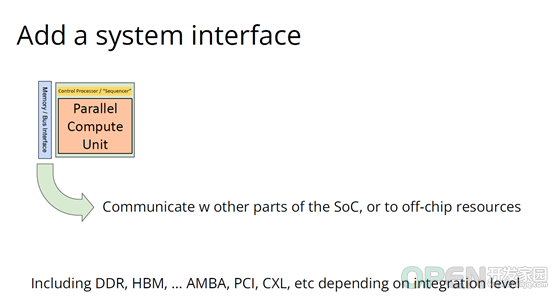

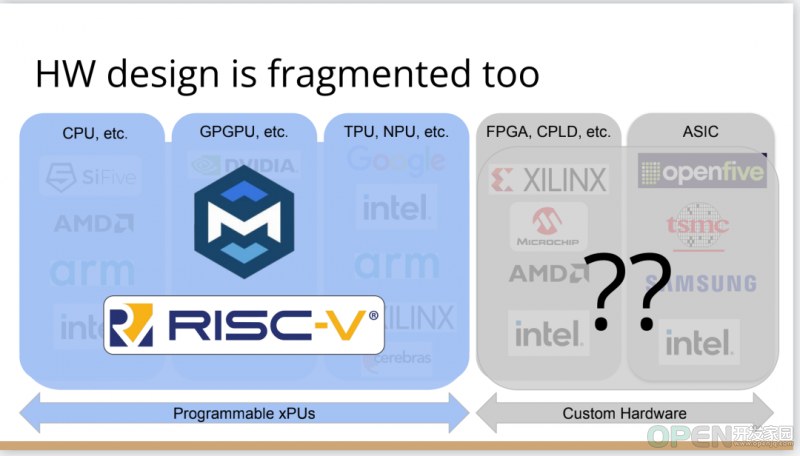

作者|Chris Lattner 翻译|胡燕君、周亚坤 发表了一篇文章里作专门论述 。1 为什么需要下一代编译器和编程语言 首先,计算机行业需要更好的硬件抽象,硬件抽象是允许软件创新的方式,不需要让每种不同设备变得过于专用化。 其次,我们需要支持异构计算,因为要在一个混合计算矩阵里做矩阵乘法、解码JPEG、非结构化计算等等。然后,还需要适用专门领域的语言,以及普通人也可以用的编程模型。 最后,我们也需要具备高质量、高可靠性和高延展性的架构。 我很喜欢编译器,很多人根据编译器在做应用,我也很尊重这一点。可以说,他们在开发下一代神经网络,而不仅仅只想做编译器。大家可以合作,这样一来就意味着他们需要可用的环境和可用的工具。2 传统编译器的设计和挑战 3 构建适用专用领域的架构 4 加速器的本质和演进 虽然我能理解这种做法,但这阻碍了行业发展,导致使用这些工具变得更加困难。 因此,要减少社区中愿意容忍和使用这些工具的人。我的主张是创新编程模型,发展新的应用程序,通过不断创新推动行业向前发展。我们应该对此过程所需的一切实行标准化,通过标准化能够快速完成工作,然后就可以把时间花在真正重要的事情上。 5 编译器的创新机会 6 总结 (本文已获取编译授权,视频链接:https://www.youtube.com/watch?v=4HgShra-KnY) 其他人都在看 欢迎下载体验OneFlow v0.7.0最新版本: https://github.com/Oneflow-Inc/oneflow/ 本文分享自微信公众号 - OneFlow(OneFlowTechnology)。

免责声明:

1. 本站所有资源来自网络搜集或用户上传,仅作为参考不担保其准确性!

2. 本站内容仅供学习和交流使用,版权归原作者所有!© 查看更多

3. 如有内容侵害到您,请联系我们尽快删除,邮箱:kf@codeae.com

![]() 游戏开发

发布于:2022-04-26 16:07

|

阅读数:662

|

评论:0

游戏开发

发布于:2022-04-26 16:07

|

阅读数:662

|

评论:0

QQ好友和群

QQ好友和群 QQ空间

QQ空间