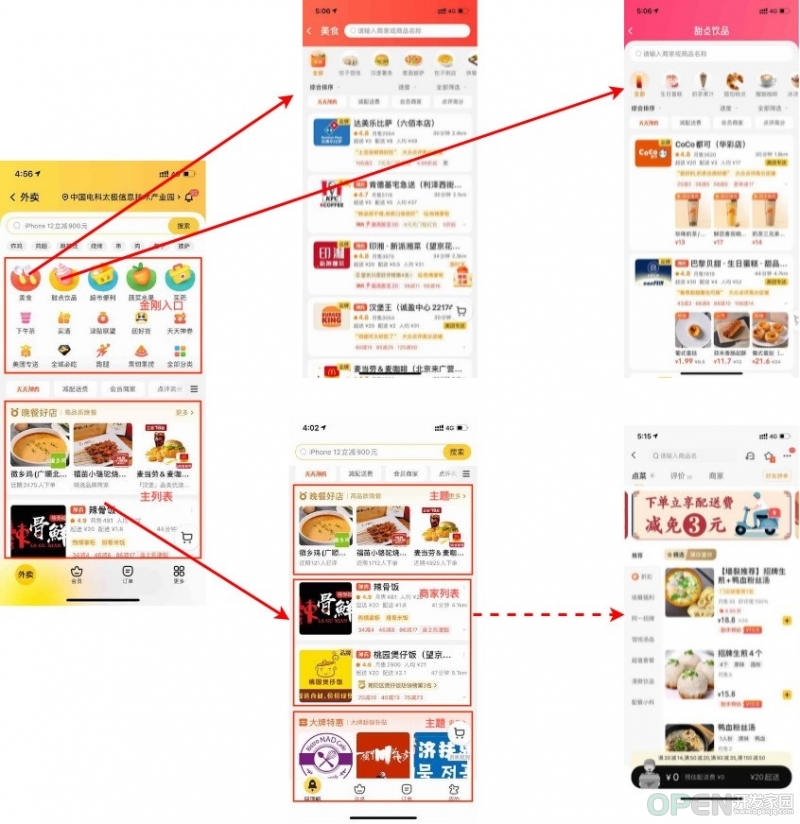

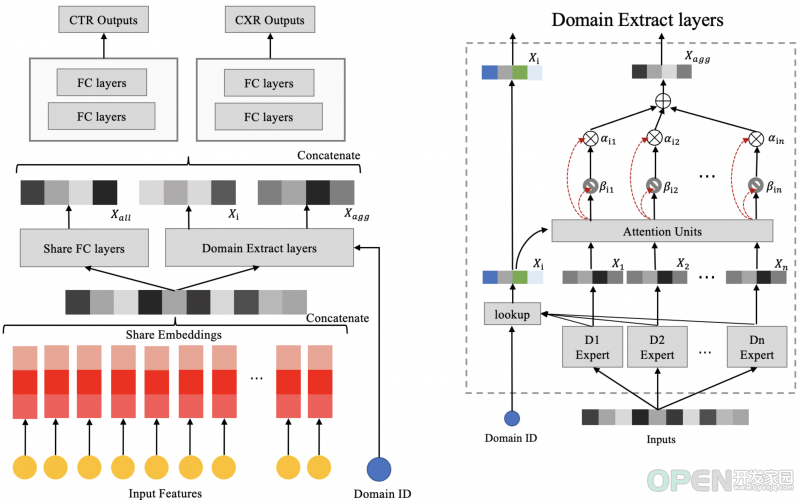

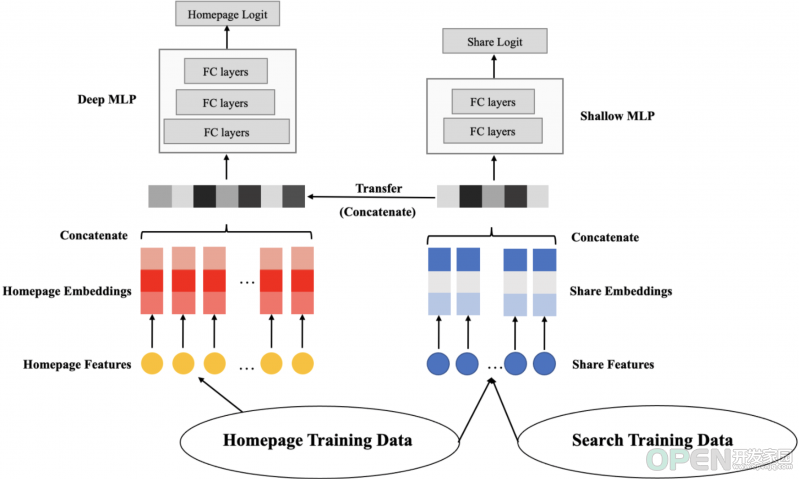

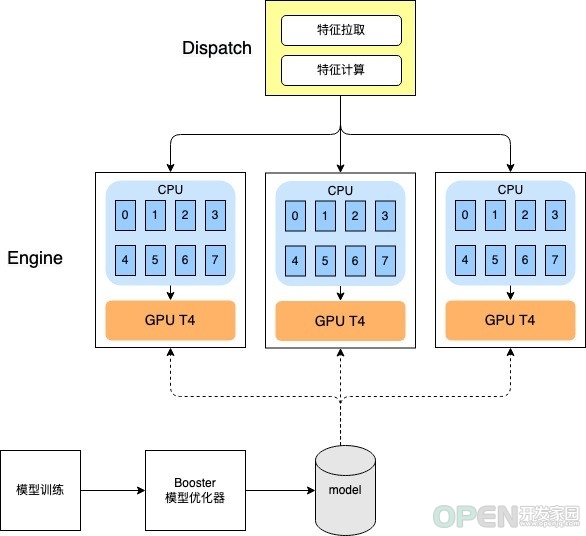

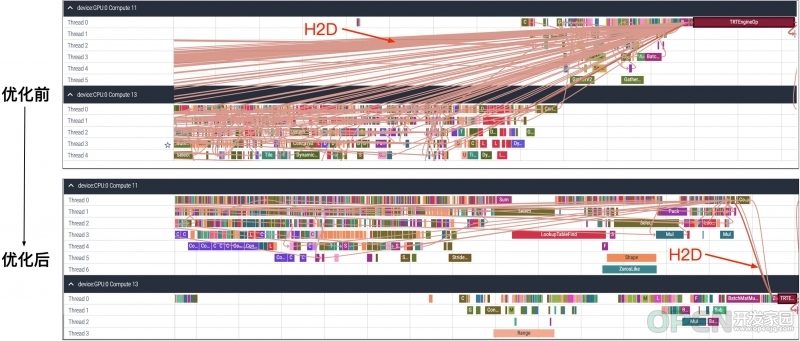

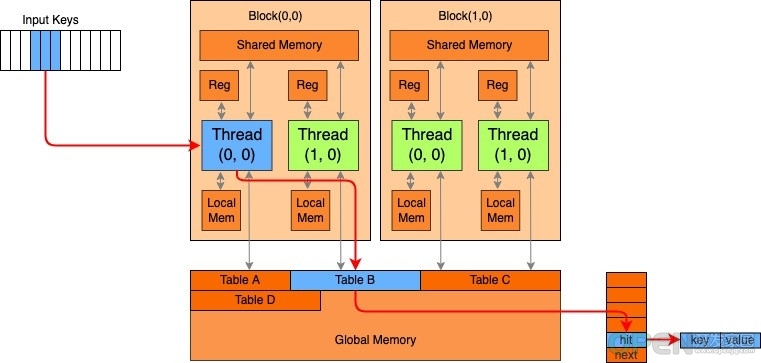

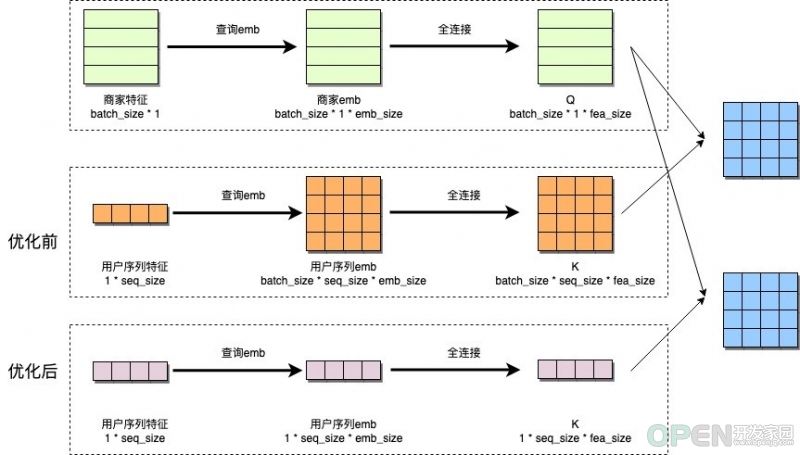

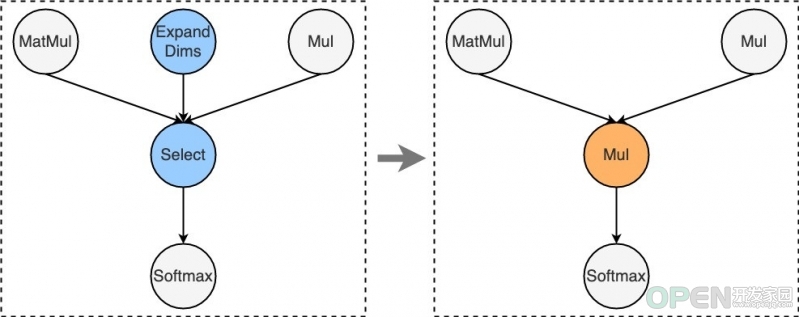

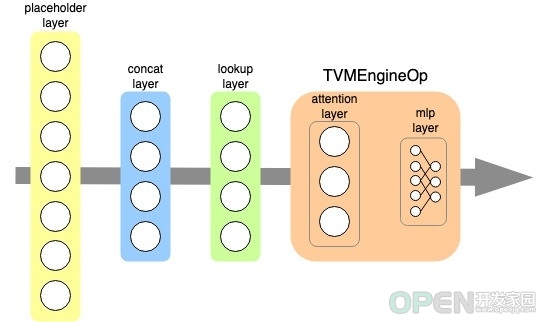

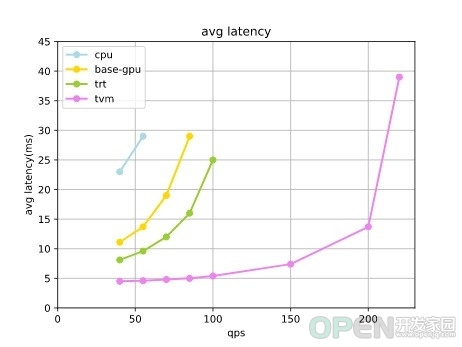

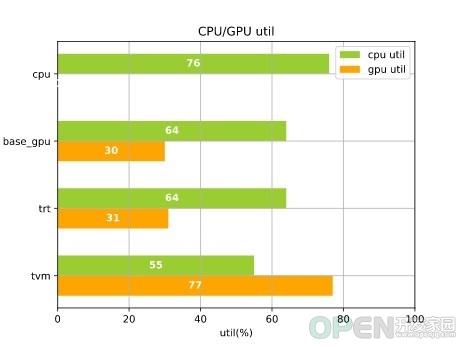

GPU等专用芯片以较低的成本提供海量算力,已经成为机器学习领域的核心利器,在人工智能时代发挥着越来越重要的作用。如何利用GPU这一利器赋能业务场景,是很多技术研发者都要面临的问题。本文分享了美团外卖搜索/推荐业务中模型预估的GPU架构设计及落地的过程,希望能对从事相关应用研发的同学有所帮助或启发。1 前言 2 背景 3 外卖搜推场景下的精排模型 3.1 精排模型的设计思路 首页推荐与各金刚入口推荐各维护一个精排模型,不仅维护成本高而且训练数据割裂,导致精排模型不能捕捉到用户在所有推荐场景的兴趣。 推荐场景的精排模型只使用推荐场景的训练样本,未利用用户在其他重要入口的训练样本,比如搜索、订单页,模型只学习到用户在局部场景的偏好信息。 推荐场景的训练样本中存在Position Bias问题,具体是指用户点击一个商家,有可能只是因为该商家在推荐Feeds中排序位置比较靠前,而非因为用户对此商家真正感兴趣,此类Bias会引起模型训练有偏。 多目标之间存在贝叶斯约束,网络结构中未考虑,CXR=CTR × CVR,CXR预估值应比CTR小,模型在验证集上会出现CXR比CTR还高的现象,预估不准确。 基于此,在2021年,美团外卖搜推场景提出了向超越单体的多模型统一演进、逐步实现“One Model to Serve All”的思想,这一理念在模型设计中具体体现在: CTR/CXR多目标的融合,实现多目标预测的模型统一。 场景专家网络与Attention网络的融合,实现不同流量入口之间的模型泛化和统一。 领域专属网络和共享网络的融合,实现推荐场景向搜索场景的迁移学习。 3.2 模型应用的特点与挑战 ① 需求层面 模型结构 :如前文介绍,外卖场景下的精排模型的稠密网络部分相对复杂,单次推理的FLOPs达到26M;而模型的稀疏部分经过大量的优化,体积得到了有效的控制,模型规模在10G以内。 服务质量要求 :推荐服务作为经典的高性能To C场景,业内大部分同类系统的超时控制在百毫秒量级,分解到预估服务,超时一般需要控制在十毫秒的量级。 ② 软件框架层面 开发框架 :模型开发采用TensorFlow框架[1]。作为主流的深度学习第二代框架,TensorFlow具备强大的模型表达能力,这也导致其算子粒度比较小,这一特点无论是对CPU还是GPU架构都会带来很大的额外开销。 在线服务框架 :采用TensorFlow Serving框架[2]。基于此框架,可将离线训练好的机器学习模型部署到线上,并利用rpc对外提供实时预估服务。TensorFlow Serving支持模型热更新及模型版本管理,主要特点是使用灵活,性能较好。 ③ 硬件层面 机型特性 :美团基于提升算力密度的考量,在预估服务采用了GPU BOX机型。相对于传统的GPU插卡机型,这一类机型每张GPU卡配套的CPU和内存相对有限,这需要我们在设计在线服务时,精细化的考量CPU、GPU上的计算和数据分布,达到更好的利用率均衡。 GPU固有属性 :GPU kernel大体上可以划分为传输数据、kernel启动、kernel计算等几个阶段[3],其中每个kernel的启动需要约10us左右。因此,GPU预估会面临一个普适问题,大量的小算子导致每个kernel的执行时间很短,kernel启动的耗时占了大部分。相邻的kernel之间需要通过读写显存进行数据的传输,产生大量的访存开销。而GPU的访存吞吐远远低于计算吞吐,导致性能低下,GPU的利用率并不高。 稠密网络部分计算复杂度高,相对的,稀疏网络在模型设计环节经过了大量的优化,体积相对较小。 使用GPU BOX机型,单GPU卡的CPU配额受限,需要针对性优化CPU的计算负荷。 基于这两个特点,我们在面向GPU的优化实践中就可以更具针对性了。4 模型服务架构概览 系统关键角色 Dispatch :承担着特征获取和特征计算的职能,如前文所述,美团使用GPU BOX机型搭建预估服务,推理计算的CPU资源本身就十分吃紧,因此自然会考虑将在线特征工程部分独立部署,避免CPU资源的抢占。本部分和GPU实践关系不大,不是本文的重点。 Engine :承担着模型在线推理的职能,通过RPC的方式输入特征矩阵、输出预估结果。采用GPU BOX机型(单容器8核+1 NVIDIA Tesla T4),平均响应时间需控制在20ms以内,下文所述GPU优化实践主要面向这一模块的特点进行。 Booster :在模型更新过程中离线执行的模型优化器,内部以Optimizer插件的方式,混合了手工优化器插件和DL编译优化器插件,是下文所述GPU优化操作的执行者。 5 GPU优化实践 系统优化 :一般指通过对计算、存储、传输的调度,使CPU+GPU的异构硬件体系可以更有效率的协同和被使用。典型的系统优化包括:计算优化 :一般指面向硬件特性,优化模型前向推理网络的结构设计和算子执行逻辑,使模型推理计算在GPU上的计算开销更小,效率更高。典型的计算优化包括:5.1 系统优化 5.1.1 设备摆放 5.1.2 All On GPU 5.1.3 算子融合 特定算子手动融合。例如模型训练阶段中,针对一个Embedding Table会有多个Node访问,在线预估阶段可将其融合成一个Node,即查询Node和Embedding Table一一对应。此后可进一步融合算子,一个Node负责查询多个Embeddding Table。 常见算子自动融合,主要是利用TensorFlow Grappler[4]优化器进行算子自动融合。 利用深度学习编译器自动融合,下文会详细进行介绍。 5.2 计算优化 5.2.1 FP16低精度优化 5.2.2 broadcast优化 5.2.3 高性能库应用 5.3 基于DL编译器的自动优化 5.3.1 基于TensorRT的尝试 ① 手动切分子图 ② 算子替换 5.3.2 基于TVM的尝试 6 性能表现与分析 只利用CPU进行预估计算时,极限qps为55,此时CPU利用率已经高达76%,成为瓶颈。 利用常规手工优化(设备摆放+算子融合+Broadcast优化+高性能库)的GPU预估时,相同qps下latency大幅降低,且可以将极限qps提升至85(较CPU版提升55%)。到达极限吞吐时GPU利用率并不高,瓶颈仍旧为CPU利用率。 利用TensorRT优化预估(手工优化+TensorRT+FP16)时,得益于图编译优化,相同qps下latency降低约40%。由于瓶颈仍为CPU,极限吞吐未变化。 利用TVM优化预估(手工优化+TVM+FP16+All On GPU)时,将所有OP都放置于GPU计算,CPU只负责基本的RPC,极大缓解了CPU配额的瓶颈。相同qps下latency大幅降低约70%,极限吞吐大幅提升约120%。到达极限吞吐时,GPU利用率较高,成为瓶颈。 经过一系列优化,整体吞吐提升约4倍(qps从55->220),优化效果十分明显。7 总结 8 作者简介 杨杰、俊文、瑞东、封宇、王超、张鹏等,来自到家事业群/到家研发平台/搜索推荐技术部。 王新、陈卓、駃飞等,来自基础研发平台/数据科学与平台部/数据平台中心。 9 参考文献 [1] https://www.usenix.org/system/files/conference/osdi16/osdi16-abadi.pdf [2] https://www.tensorflow.org/tfx/guide/serving [3] https://docs.nvidia.com/cuda/cuda-c-programming-guide/index.html [4] https://www.tensorflow.org/guide/graph_optimization [5] https://en.wikipedia.org/wiki/Half-precision_floating-point_format [6] https://www.nvidia.com/en-us/data-center/tensor-cores/ [7] https://www.intel.com/content/www/us/en/develop/documentation/get-started-with-mkl-for-dpcpp/top.html [8] https://www.nvidia.com/en-us/data-center/tensor-cores/ [9] https://docs.nvidia.com/cuda/cublas/index.html [10] https://developer.nvidia.com/zh-cn/cudnn [11] https://docs.nvidia.com/deeplearning/frameworks/tf-trt-user-guide/index.html [12] https://tvm.apache.org/docs/ [13] https://www.tensorflow.org/xla 阅读美团技术团队更多技术文章合集 | 在公众号菜单栏对话框回复【2021年货】、【2020年货】、【2019年货】、【2018年货】、【2017年货】等关键词,可查看美团技术团队历年技术文章合集。

![]() 游戏开发

发布于:2022-03-07 10:01

|

阅读数:423

|

评论:0

游戏开发

发布于:2022-03-07 10:01

|

阅读数:423

|

评论:0

QQ好友和群

QQ好友和群 QQ空间

QQ空间